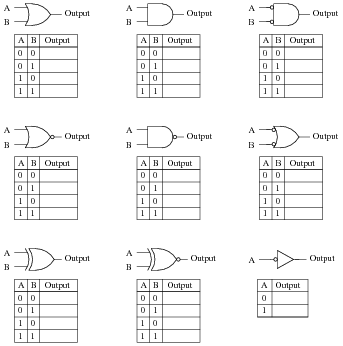

通过名称识别这些逻辑门中的每一个,并完成各自的真相表:gydF4y2Ba

|

|

|

|

为了让学生熟悉标准的逻辑门类型,我喜欢让他们每天练习识别和真值表。学生需要能够一眼认出这些逻辑门类型,否则他们将很难分析使用它们的电路。gydF4y2Ba

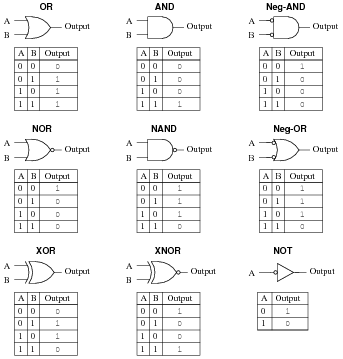

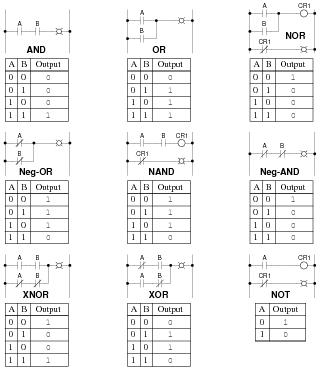

通过名称(以及或,或,或等)来识别这些中继逻辑函数中的每一个并完成各自的真相表:gydF4y2Ba

|

|

|

|

为了熟悉标准交换机联系配置的学生,我喜欢每天使用识别和真理表的练习。学生需要能够一目了然地识别这些梯形逻辑子电路,否则它们将难以分析使用它们的更复杂的继电器电路。gydF4y2Ba

检查每个布尔表达式,并确定每个是否是一个gydF4y2Ba和产品的gydF4y2Ba,或者一个gydF4y2Ba总和的产品gydF4y2Ba:gydF4y2Ba

$ $ (B + \眉题{C} + D)(\眉题{一}+ B) $ $gydF4y2Ba

$$ a \ overline {b} \ overline {c} + \ overline {a} bc $$gydF4y2Ba

$ $ (X + \眉题{Y} + \眉题{Z})(\眉题{Y} + Z)(\眉题{X} + Y) $ $gydF4y2Ba

$ $ \眉题{M} \眉题{N} \眉题{O} +锰\眉题{O} + M \眉题{N} $ $gydF4y2Ba

$ $ (X + \眉题{Y + Z})(\眉题{Y + \眉题{Z}}) $ $gydF4y2Ba

$ $ \眉题{ABC} + \眉题C $ $ {B}gydF4y2Ba

$ $ (B + \眉题{C} + D)(\眉题{一}+ B) \ POS $ $gydF4y2Ba

$ $ \眉题{B} \眉题{C} + \眉题公元前{一}\ SOP $ $gydF4y2Ba

$ $ (X + \眉题{Y} + \眉题{Z})(\眉题{Y} + Z)(\眉题{X} + Y) \ POS $ $gydF4y2Ba

$$ \ overline {m} \ overline {n} \ overline {o} + mn \ overline {o} + m \ overline {n} o \ sop $$gydF4y2Ba

最后两个表达式是“技巧”问题:技术上是求和变量的乘积和乘(积)变量的和,但不遵循“标准”的POS和SOP形式,因为它们都有很长的互补条:gydF4y2Ba

$ $ (X + \眉题{Y + Z})(\眉题{Y + \眉题{Z}}) $ $gydF4y2Ba

$ $ \眉题{ABC} + \眉题C $ $ {B}gydF4y2Ba

对于正确遵循SOP或POS规范形式的表达式,不应涵盖多个变量的互补栏!gydF4y2Ba

即使你的学生之前从未听说过布尔代数,他们仍然应该能够确定前四个表达式中哪些是SOP,哪些是POS。如果在这一点上有任何困惑,请让你的学生分别定义“sum”和“product”的含义。然后讨论一个表达式是和(倍数)的乘积(单数)或乘积(倍数)的和(单数)是什么意思。gydF4y2Ba

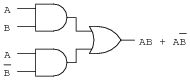

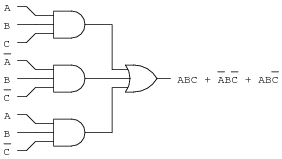

乘积和布尔表达式都遵循相同的一般形式。因此,它们的等效逻辑门电路同样遵循一种常见的形式。将每个SOP表达式转换为对应的逻辑门电路:gydF4y2Ba

$ $ AB + \眉题{B} $ $gydF4y2Ba

$ $ \眉题{B} + \眉题{A} $ $gydF4y2Ba

$ $ + ABC \眉题{A} \眉题{C} + AB \眉题{C} $ $gydF4y2Ba

|

|

|

|

|

|

BOOLEAN SOP转换为门电路的翻译不应困难。这个问题的重点是让学生以积和的形式思考,这样他们就会为下一步做好准备:将这个概念与真值表联系起来。gydF4y2Ba

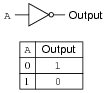

尽管很少这样做,但通过描述为了产生“高”输出必须满足哪些条件,用语言表达真值表是可能的。gydF4y2Ba

以这个简单的真值表为例,对于一个逆变电路:gydF4y2Ba

|

|

对于这个真理表,我们可以说输出在低点时变高。不同的方式说这将是说“产出是gydF4y2Ba真正的gydF4y2Ba当\({}\ \酒吧)gydF4y2Ba真正的gydF4y2Ba”。gydF4y2Ba

让我们看另一个例子,这次是与门:gydF4y2Ba

|

|

对于真值表,我们可以说当A和B都是高值时输出会变高。另一种说法是:“当A为真,B为真时,输出为真。”使用半布尔半语言的描述:gydF4y2Ba

|

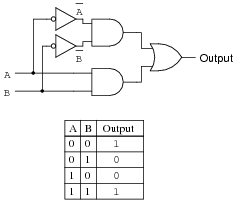

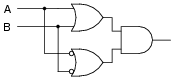

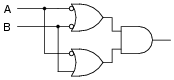

检查逻辑门电路和对应的真值表:gydF4y2Ba

|

|

用文字表达真值表的功能。必须满足哪些布尔条件(“true”)才能使输出假定高状态?gydF4y2Ba

当\(\ bar {a} \)为true并且\(\ bar {b})为true,或者当a为true并且b为true时:gydF4y2Ba

$ $(\眉题和{}\ \ \眉题{B}) \ \(和\ \ B)或$ $gydF4y2Ba

“口头”表达真值表条件是一种向学生介绍从它们推导布尔表达式的概念的方法。gydF4y2Ba

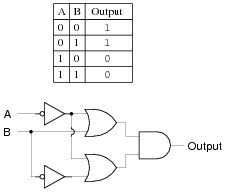

开发这个真理表的口头描述,指定必须满足的条件(“gydF4y2Ba真正的gydF4y2Ba"在布尔意义上),以使输出假定一个高状态:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

对真值表也做同样的操作:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

对于第一个真值表:当A为真且\(\bar{B}\)为真且C为真时,该电路的输出是高的:gydF4y2Ba

$$ a \ and \ \ \ overline {b} \和\ c $$gydF4y2Ba

对于第二个真理表:当\(\ bar {a} \)为true并且\(\ bar {b} \)为true,c为true,或者\(\ bar {a} \)是真,b是真实的,\(\ bar {c} \)是真的:gydF4y2Ba

$ $(\眉题和{}\ \ \眉题{B} \ \ C)或\ \(\眉题{一}\ \ B \和\ \眉题{C}) $ $gydF4y2Ba

后续问题:你怀疑我们可以为每个真相表编写正式的布尔表达式吗?这些表达是什么,以及它们会在哪些形式(SOP或POS)?gydF4y2Ba

我发现这种“语言”方法很好地向学生介绍了从真值表推导布尔表达式的概念。gydF4y2Ba

一定要问你的学生他们为这两个真值表推导出了什么布尔表达式。如果答案是“口头的”,这对他们来说应该不难!gydF4y2Ba

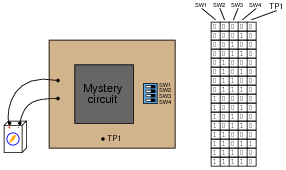

假设你面临的任务是为一个逻辑电路写一个布尔表达式,它的内部结构是未知的。电路有四个输入-每一个由它自己的微开关的位置设置-和一个输出。通过对所有可能的输入开关组合进行实验,并使用逻辑探针“读取”输出状态(在测试点TP1),您可以写出以下描述电路行为的真值表:gydF4y2Ba

|

|

根据电路的真值表“描述”,为电路写出一个合适的布尔表达式。gydF4y2Ba

要使事情更容易,我将把每个交换机与唯一的字母字母联系起来:gydF4y2Ba

现在,布尔表达式:gydF4y2Ba

$ $ AB \眉题}{C D $ $gydF4y2Ba

这道题让学生预览gydF4y2Basum-of-productsgydF4y2Ba符号。通过检查真相表,他们应该能够确定只有一个交换机设置(布尔值)的组合提供“1”输出,并且有点思考它们应该能够将此布尔产品声明拼凑在一起。gydF4y2Ba

虽然这个问题可能会为某些学生(特别是数学推理技能弱者)提前,但它在课堂讨论中的所有人都是教育,在那里学生和教练的思想都暴露。raybet电子竞技竞猜gydF4y2Ba

为此真值表编写一个布尔SOP表达式,然后尽可能简化该表达式,并绘制等效于此简化表达式的逻辑门电路:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

原始SOP表达式:gydF4y2Ba

$ $ \眉题{A} \眉题C {} \ AB + \ \眉题{C} $ $gydF4y2Ba

简化表达式和门电路:gydF4y2Ba

$ $ B \眉题{C} $ $gydF4y2Ba

|

|

挑战您的学生直接用逻辑门实现原始的SOP表达式(三输入门可以使用)。gydF4y2Ba

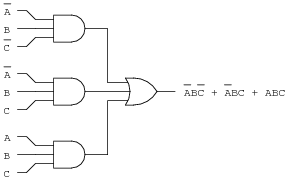

为此真理表编写SOP表达式,然后绘制与该SOP表达式对应的门电路图:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

最后,用布尔代数对该表达式进行简化,并在此基础上绘制出简化的门电路。gydF4y2Ba

原始SOP表达式及门电路:gydF4y2Ba

|

|

简化表达式和门电路:gydF4y2Ba

|

|

与您的学生讨论布尔代数作为电路简化工具的实用程序。要求您的学生比较原始和减少的逻辑门电路,并评论这种性能度量,作为可靠性,功耗,最大操作速度等。gydF4y2Ba

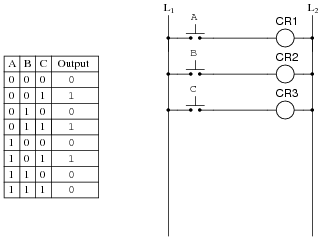

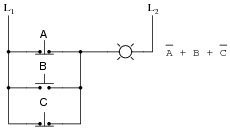

对这个真值表写一个SOP表达式,然后画一个对应于该SOP表达式的梯子逻辑(继电器)电路图:gydF4y2Ba

|

|

使用继电器CR1、CR2和CR3的触点实现SOP逻辑功能。已提供部分梯形逻辑图给您。gydF4y2Ba

最后,使用布尔代数对该表达式进行简化,并根据这个新的(简化的)布尔表达式绘制简化的梯形逻辑图。当决定减少布尔表达式的“多远”时,选择一种形式,使简化的梯形逻辑图中继电器触点的数量最少。gydF4y2Ba

原始SOP表达式及继电器电路:gydF4y2Ba

|

|

减少表达和继电器电路:gydF4y2Ba

|

|

与您的学生讨论布尔代数作为电路简化工具的实用程序。要求您的学生比较原始和减少的逻辑门电路,并评论这种性能度量,作为可靠性,功耗,最大操作速度等。gydF4y2Ba

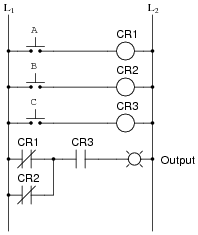

设计尽可能简单的继电器电路(即使用最少的触点)来实现以下真值表:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

最简单的继电器电路:gydF4y2Ba

|

|

让您的学生在设计继电器电路时显示所有工作。通过呈现他们的思想流程,不仅您帮助他们巩固他们的学习,而且还通过允许他们从同行学习来帮助其他学生更好地了解。gydF4y2Ba

和的乘积布尔表达式都遵循相同的一般形式。因此,它们的等效逻辑门电路同样遵循一种常见的形式。将每一个POS表达式转换为其等效的逻辑门电路:gydF4y2Ba

$$(a + b)(\ overline {a} + \ overline {b})$$gydF4y2Ba

$$(\ ovline {a} + \ overline {b})(\ overline {a} + b)$$gydF4y2Ba

$ $ (A + B + C)(\眉题{一}+ B + \眉题{C}) (A + B + \眉题{C}) $ $gydF4y2Ba

|

|

|

|

|

|

从布尔POS到门电路的转换应该不难。这个问题的重点是让学生思考“和的乘积”的形式,这样他们就会为下一步做好准备:将这个概念与真值表联系起来。gydF4y2Ba

和的乘积布尔表达式都遵循相同的一般形式。因此,它们的等效逻辑门电路同样遵循一种常见的形式。将每一个POS表达式转换为其等效的逻辑门电路:gydF4y2Ba

$ $ (A + B) (A + \眉题{B}) $ $gydF4y2Ba

$$(a + \ overline {b})(\ overline {a} + b)$$gydF4y2Ba

$ $ (A + B + C)(\眉题{一}+ B + \眉题{C}) (A + B + \眉题{C}) $ $gydF4y2Ba

|

|

|

|

|

|

从布尔POS到门电路的转换应该不难。这个问题的重点是让学生以积和的形式思考,这样他们就会为下一步做好准备:将这个概念与真值表联系起来。gydF4y2Ba

在一个SOP表达式中,要使表达式的总值等于1的最小要求是至少有一个乘积项必须等于1。例如,在下面的SOP表达式中,我们知道如果ABC = 1或如果A\(\bar{B}\)\(\bar{C}\) = 1或如果AB\(\bar{C}\) = 1,该值将等于1:gydF4y2Ba

$ $ ABC \ + \ \眉题{B} \眉题C {} \ AB + \ \眉题{C} $ $gydF4y2Ba

POS表达式等于0的最低要求是什么?以下面的POS表达式为例:gydF4y2Ba

$$(a + b + c)(a + \ overline {b} + c)(\ overline {a} + b + c)$$gydF4y2Ba

至少,要让这个表达式等于0,需要做什么?gydF4y2Ba

求和项中至少有一项必须等于零。gydF4y2Ba

随访问题:为了使这些术语之一等于零,因此使整个表达式等于零,关于每个布尔文字必须是真的(agydF4y2Ba文字gydF4y2Ba是一个变量或一个变量的补数)在至少一个求和项内?gydF4y2Ba

这个问题预示着从真值表推导出POS表达式。它也平行于实数代数中的多项式根的主题。例如,多项式xgydF4y2Ba2gydF4y2Ba−2x−8可被分解为:gydF4y2Ba

|

如果我们将这个等式设置为零,则gydF4y2Ba根gydF4y2Ba等式将是4和-2:x的值将使术语之一等于零。gydF4y2Ba

当你的学生试图理解POS表达式的时候,你可能会发现这个“正常”代数的迷你复习对你的学生是有帮助的。gydF4y2Ba

检查下面的真值表:gydF4y2Ba

|

|

我们知道这个表代表了与非门的功能。但是假设我们希望为这个门生成一个布尔表达式,就像我们不知道它已经是什么一样,并且我们选择基于真值表中的所有“high”输出条件生成一个SOP表达式:gydF4y2Ba

$$ \ overline {a} \ overline {b} + \ overline {a} b + a \ overline {b} $$gydF4y2Ba

就一扇门来说工作量太大了,不是吗?这个真值表的输出大部分是1,这导致我们不得不编写一个相对较长的SOP表达式。如果我们有一种技术从单gydF4y2Ba零gydF4y2Ba此表中的输出条件?如果我们有这样的技术,我们所产生的布尔表达将在其中有很多术语!gydF4y2Ba

我们知道“负或”门具有与“与”门完全相同的功能。我们还知道负或门的布尔表示是\(\bar{a}\)+\(\bar{B}\)。如果有一种技术可以从真值表的“0”输出导出布尔表达式,那么这个实例应该适合它!gydF4y2Ba

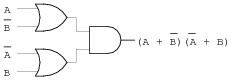

现在,检验下面的真值表和逻辑门电路:gydF4y2Ba

|

|

从这里所示的门电路推导出一个布尔表达式,然后将该表达式与该电路所示的真值表进行比较。在这个例子(和前面的例子)中,您是否看到了一个模式,它会建议一个直接从真值表中导出布尔表达式的规则?gydF4y2Ba

提示:规则涉及gydF4y2BaProduct-of-SumsgydF4y2Ba的形式。gydF4y2Ba

第二门电路布尔表达式:gydF4y2Ba

$$(\ ovline {a} + b)(\ ovline {a} + \ overline {b})$$gydF4y2Ba

挑战问题:我们知道\(\ ovline {ab})也是第一门(nand)电路的有效布尔表达式,除了\(\ bar {a} \)+ \(\ bar {b}\)。是否有规则可以考虑直接从真相表中派生\(\ ovline {ab})?您可以使用布尔定律和规则将此规则应用于第二门电路,并使用布尔定律和规则进行操作以获取表达式(\(\ bar {a} \)+ b)(\(\ bar {a} \)+(\ bar {b} \))?gydF4y2Ba

这个问题的目的,如果你现在还不清楚的话,是让学生“发现”从真值表中导出POS表达式的技术,基于对所有“低”输出状态的评估。gydF4y2Ba

更高级的学生应该会喜欢这个挑战性的问题,因为它允许使用与第一个相似的规则生成布尔表达式:table-to-SOP。gydF4y2Ba

检查这个真相表,然后写下描述输出的SOP和POS布尔表达式:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

对于这个真值表,哪个布尔表达式更简单?哪一个更容易简化为最简单的形式(为了创建一个门电路来实现它)?gydF4y2Ba

SOP表达:gydF4y2Ba

$ $ \眉题{}\眉题{B} \眉题{C} + \眉题{A} \眉题{C} + \眉题{B} C + AB \眉题{C} $ $gydF4y2Ba

POS表达式:gydF4y2Ba

$$(a + b + \ overline {c})(a + \ overline {b} + \ overline {c})(\ overline {a} + b + c)(\ overline {a} + \ overline {b} +\ overline {c})$$gydF4y2Ba

注意:在确定哪个表达式更简单之前,请记住必须在应用任何标准布尔简化规则之前分发POS表达式。gydF4y2Ba

后续问题:将和对比与真相表生成SOP与POS表达的过程进行比较。您在编写每种类型的表达式时寻找哪些州(1或0)?解释为什么。gydF4y2Ba

挑战问题:您认为哪些真值表场景会“偏爱”SOP表达式而不是POS表达式,反之亦然?换句话说,在什么条件下真值表会产生更简单的SOP表达式,而不是更简单的POS表达式?gydF4y2Ba

这个问题实际上是要求学生比较SOP和POS表达式,而不是针对给定真值表的问题。答案中给出的实际表达仅用于“练习”,因此学生可以检查自己的作业。的gydF4y2Ba真正的gydF4y2Ba答案与后续问题和挑战问题相关!gydF4y2Ba

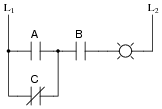

为这个真值表写一个POS表达式,然后画一个梯形逻辑电路对应该表达式:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

要求学生对比写这个函数的POS表达式和SOP表达式的难度。复杂性上的差异是巨大的!同时,请他们比较电路等效的每一种形式的布尔表达式的真值表。哪种形式的电路具有更少的门?gydF4y2Ba

为此真理表编写一个布尔表达式,然后尽可能简化该表达式,并绘制等效于此简化表达式的逻辑门电路:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

原始POS表达式:gydF4y2Ba

$ $ (A + \眉题{B} + C)(\眉题{一}+ B + C) $ $gydF4y2Ba

简化表达式和门电路:gydF4y2Ba

|

|

挑战您的学生直接使用逻辑门实现原始POS表达式(可以使用三输入门)。答案中显示的“简化”POS表达式在实际门电路环境中真的更简单吗?问问你的学生,这个比较对于布尔简化技术及其在真实电路中的应用有什么启示。gydF4y2Ba

为此真理表编写一个布尔表达式,然后尽可能简化该表达式,并绘制等效于此简化表达式的逻辑门电路:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

原始POS表达式:gydF4y2Ba

$ $(\眉题{一}+ \眉题{B} + C)(\眉题{一}+ \眉题{B} + \眉题{C}) $ $gydF4y2Ba

简化门电路:gydF4y2Ba

|

|

挑战问题:其他单个门类型将满足真相表(除了负面或门外)吗?gydF4y2Ba

挑战您的学生直接使用逻辑门实现原始POS表达式(可以使用三输入门)。在实际门电路的背景下,答案中显示的“简化”POS表达式是否更简单?问问你的学生,这个比较对于布尔简化技术及其在真实电路中的应用有什么启示。gydF4y2Ba

为异或函数编写两个布尔表达式,一个以SOP形式编写,另一个以POS形式编写。通过布尔代数简化证明这两个表达式确实是等价的。然后,画出最简单的梯形逻辑电路来实现此功能。gydF4y2Ba

SOP形式:\(\bar{A}\)B + A\(\bar{B}\)gydF4y2Ba

POS形式:(\(\ bar {a} \)+ \(\ bar {b} \))(a + b)gydF4y2Ba

我会让你们做代数运算来证明这两个表达式是等价的!gydF4y2Ba

|

|

问你的学生他们中有多少人用真理表来解决这个问题。这是一个有用的提示,因为EX-OR门的真理表易于记住(或查找),并且它为轻松构建SOP或POS表达提供了基础。gydF4y2Ba

异或函数在逻辑电路中非常非常有用。值得学生花时间去理解如何用布尔形式表示它(不,也不是用那个有趣的⊕符号,而是用一种适用于所有布尔代数标准定律的形式来表示它!)gydF4y2Ba

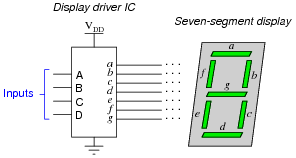

一个gydF4y2Ba七个段解码器gydF4y2Ba是一种数字电路,设计用于驱动一个非常常见的数字显示设备类型:一组LED(或LCD)段,其在四位代码的命令下呈现数字0到9:gydF4y2Ba

|

|

显示驱动IC的行为可以用一个有7个输出的真值表来表示:7段显示(a到g)的每段都有一个真值表。下表中,“1”的输出表示有活动的显示段,而“0”的输出表示无活动的显示段:gydF4y2Ba

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

写出输出a、b、c和e的未简化的SOP或POS表达式(选择最合适的形式)。gydF4y2Ba

原始(无意义的)表达式:gydF4y2Ba

$ $ = (D + C + B + \眉题{一})(D + \眉题{C} + B + a) $ $gydF4y2Ba

$$ b =(d + \ overline {c} + b + \ overline {a})(d + \ overline {c} + \ overline {b} + a)$$gydF4y2Ba

$$ C = D + C + \ overline {B} + A $$gydF4y2Ba

$ $ e = \眉题{D} \眉题C{} \眉题{B} \眉题{一}+ \眉题{D} \眉题B C{} \眉题{一}+ \眉题{D} CB \眉题{一}+ D \眉题C{} \眉题{B} \眉题{一}$ $gydF4y2Ba

挑战问题:用布尔代数法则把上面的每一个表达式简化成最简单的形式。gydF4y2Ba

这示出了SOP和POS布尔形式的一个非常实际的例子,为什么需要简化以将所需栅极的数量降低到实用最小值。gydF4y2Ba

| 别光坐在那儿!构建的东西! !gydF4y2Ba |

学习分析继电器电路需要大量的学习和实践。通常情况下,学生通过做大量的例题并对照课本或老师提供的答案进行练习。虽然这很好,但还有更好的方法。gydF4y2Ba

你会学到更多gydF4y2Ba建设和分析真实电路gydF4y2Ba让你的测试设备来提供“答案”,而不是书本或其他人。对于成功的电路构建练习,遵循以下步骤:gydF4y2Ba

始终确保电源电压水平在您计划使用的继电器线圈内的规格范围内。我建议使用PC板继电器,线圈电压适用于单电池电源(6伏是好的)。中继线圈比说,比如半导体逻辑门,所以使用“灯笼”大小6伏电池进行足够的操作寿命。gydF4y2Ba

节省时间和减少出错可能性的一种方法是,从一个非常简单的电路开始,然后在每次分析后逐步添加组件以增加其复杂性,而不是为每个实践问题构建一个全新的电路。另一种节省时间的技术是在各种不同的电路配置中重复使用相同的组件。这样,您就不必重复度量任何组件的值。gydF4y2Ba

让电子自己给你自己的“练习问题”的答案!gydF4y2Ba

这是我的经验,学生需要对电路分析变得熟练的许多实践。为此,教师通常为他们的学生提供许多实践问题来通过,并为学生提供答案来检查他们的工作。虽然这种方法使学生精通电路理论,但它无法完全教育它们。gydF4y2Ba

学生们不仅仅需要数学练习。他们还需要实际的、动手实践构建电路和使用测试设备。因此,我建议学生采取以下替代方法:学生应该gydF4y2Ba构建gydF4y2Ba他们自己的“实践问题”与真实组成部分,并尝试预测各种逻辑状态。这样,继电器理论“活着”,学生获得实际熟练程度,他们不会仅仅通过解决布尔方程或简化卡纳映射地图。gydF4y2Ba

以下这种实践方法的另一个原因是教学gydF4y2Ba科学的方法gydF4y2Ba:通过进行真实实验来检验假设(在这种情况下是逻辑状态预测)的过程。学生也将发展真正的故障排除技能,因为他们偶尔会做出电路构造错误。gydF4y2Ba

在他们开始之前,用你的课程花一些时间来审查建筑电路的一些“规则”。与您的学生以相同的古典方式讨论这些问题,您通常会讨论工作表的问题,而不是简单地告诉他们他们应该和不应该这样做。我从来没有停止过惊讶于学生在典型的讲座(教练独白)格式中掌握了指示!gydF4y2Ba

对那些可能抱怨拥有学生构建真实电路所需的“浪费”时间的指导员,而不是仅在数学上分析理论电路:gydF4y2Ba

学生上这门课的目的是什么?gydF4y2Ba

如果您的学生将使用真实的电路,那么他们应该尽可能地在真实的电路中学习。如果你的目标是培养理论物理学家,那么务必坚持抽象分析!但我们大多数人都计划让我们的学生在现实世界中做一些事情,利用我们给他们的教育。raybet电子竞技竞猜当他们将知识应用于实际问题时,花在构建真实电路上的“浪费”时间将带来巨大的回报。gydF4y2Ba

此外,让学生建立自己的实践问题教他们如何表演gydF4y2Ba主要研究gydF4y2Ba因此,使他们能够自主地继续他们的电气/电子教育。雷竞技最新appraybet电子竞技竞猜gydF4y2Ba

在大多数科学中,建立真实的实验比建立电路要困难和昂贵得多。核物理、生物、地质和化学的教授们会很乐意让他们的学生将高等数学应用到真正的实验中,而不会造成任何安全隐患,而且成本低于教科书。他们不能,但你可以。利用你的科学固有的便利,而且gydF4y2Ba让你的学生在许多真实的电路上练习他们的数学!gydF4y2Ba

根据条款和条件发布gydF4y2Ba知识共享gydF4y2Ba归因执照gydF4y2Ba

在伙伴关系gydF4y2BaSamtec.gydF4y2Ba

通过gydF4y2Ba伊格纳西奥·德·蒙迪扎巴尔gydF4y2Ba

通过gydF4y2Ba模拟设备gydF4y2Ba

通过gydF4y2Ba杰克赫兹gydF4y2Ba

通过gydF4y2Ba杰克赫兹gydF4y2Ba